# Low-Power High-Speed SRAM Circuits using Low-Swing Bit-lines

## 低振幅ビット線方式を用いた低消費電力高速SRAM

電子工学専攻 桜井研究室

修士2年 06435 服部 貞昭

### Abstract

A novel SRAM cell architecture for low-power high-speed operation is proposed that uses no low-V<sub>TH</sub> MOSFET's. An additional n-type MOSFET is connected to the source terminals of the driver MOSFET's which enables write operation with a little voltage difference between opposite bit lines. Low bit-line swing in write and read cycles reduces the power dissipation drastically. This technique is demonstrated in a 64-K SRAM fabricated in a 0.35-μm CMOS technology. Power dissipation is reduced by 1/5 in write and read cycles at 1.5V in a HSPICE simulation.

### 1. はじめに

1971年にインテルにより初めて作られたマイクロプロセッサ Intel4004は、10 μテクノロジでわずか2,300個のトランジスタから成るクロック周波数740KHzのチップであった[1]。それ以来、LSI技術は劇的な進歩を遂げ、現在では数百万個のトランジスタを積んだクロック周波数1GHzを超えるチップが製造されるに至っている。そして、ITRS(International Technology for Semiconductors)[2]によれば、LSI技術の進歩は今後10年間も同じ勢いで続くと予想されており、Table 1に示すように2011年には、約0.5Vで10GHzを超えるチップが登場する可能性がある。

| Year                | 1999 | 2002 | 2005 | 2008 | 2011 | 2014 |

|---------------------|------|------|------|------|------|------|

| Tech.(nm)           | 180  | 130  | 100  | 70   | 50   | 35   |

| Lg(nm)              | 140  | 100  | 70   | 50   | 30   | 20   |

| V <sub>dd</sub> (V) | 1.5  | 1.2  | 0.9  | 0.6  | 0.5  | 0.3  |

| Freq.(GHz)          | 1.25 | 2.1  | 3.5  | 6.0  | 10.0 | 13.5 |

| Power(W)            | 90   | 130  | 160  | 170  | 174  | 183  |

Tech.: Technology Node, Lg: Gate Length of microprocessor,

V<sub>dd</sub>: Minimum logic V<sub>dd</sub> for lowest power,

Freq.: Frequency, Power: High-performance with heatsink

Table 1 ITRS Road Map

しかし、Technology Nodeが100nmより小さい領域のデバイス実現には相当な困難が伴うと予測されている[3]。また周波数の増加、回路規模の増加に伴ってチップあたりの消費電力が増加する傾向にあり、消費電力に対して何の

対策も施さなければ200W近くになることが予想される。特にポータブル機器においては電力の削減が緊急の課題となっている。例えば、600MHzのMobile Pentiumコアの最大消費電力は21.6W[4]であり、フルサイズのノートPCの消費電力ガイドラインである12W(プロセッサと2次キャッシュの最大消費電力)[5]をすでに超えている。

プロセッサは主に論理部とメモリ部より成り、両方の消費電力を削減することが要求される。論理部は主にCMOS回路であり、ディジタルCMOS回路の消費電力は次のような式で与えられる。

$$P = p_t f_{CLK} C_L V_S V_{DD} + I_0 10^{-(V_{TH}/S)} V_{DD} \quad (1)$$

ここで、p<sub>t</sub>はスイッチング確率、f<sub>CLK</sub>はクロック周波数、C<sub>L</sub>は負荷容量、V<sub>S</sub>は信号振幅、V<sub>DD</sub>は電源電圧、I<sub>0</sub>はチップ内全トランジスタの合計幅に比例する定数、Sはサブスレッショルド係数である。第1項は負荷の充放電に要する電力であり、第2項はリーク電流による消費電力である。通常のCMOSでは第1項の動作電流の方が支配的であり、また、信号振幅は電源電圧に等しく、電力は電源電圧の2乗に比例しているので、電源電圧を減少させることが消費電力の削減に最も効果的な方法である。しかし、単に電源電圧を落とせば回路の遅延が増加するという問題が起るので、しきい値も同時に下げ最適化することにより、遅延やリーク電流の制御をする。

次にメモリ部については、論理部と同じように、単に電源電圧としきい値を下げて最適化をすることはできない。メモリ部は主にSRAM回路であり、セル内のノードにはデータが格納されている。もし、しきい値を落とせば、高負荷のビット線からMOSを通して流れるリーク電流が発生し、最悪の場合データが失われるおそれもある。また、高負荷のワード線やビット線を充電するには、充分な電流を供給する必要があり、供給電圧を著しく下げるることは難しい。

現在のSRAMの消費電力の多くは高負荷のビット線の充電に依存している。通常、書き込みを行う際には、両方のビット線を電源電圧まで引き上げた(プリチャージ)後、片方のビット線をグラウンドまで落とす。ここで、もし、ビット線をグラウンドまで落とさずに、片方のビット線よりやや低いレベルに落とすだけで書き込みを行うことができたならば、次のプリチャージに要する消費電力を大幅に削減することが可能である。この点に着目し、ビット線を低振幅で書き込みを行う方法を考案し、セル部のみのチ

ップの試作を行った。

第2章では論理部の消費電力削減法について簡単に触れる。第3章ではSRAMセルの消費電力削減法について、考案した低振幅書き込み方式を中心に述べる。また、その方式の問題点およびメモリ全体の概要についても述べる。第4章で結論とする。

## 2. 論理部の消費電力削減法

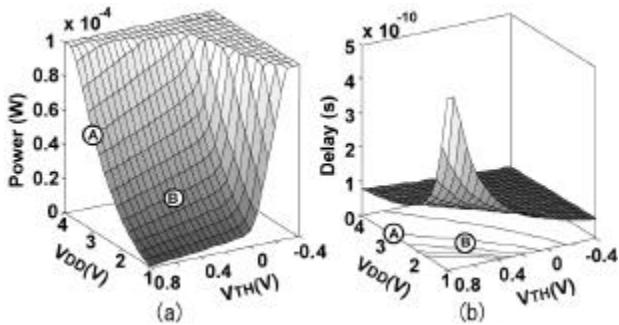

Fig. 1 (a) Power dependence on V<sub>DD</sub> and V<sub>TH</sub> (b) Delay dependence on V<sub>DD</sub> and V<sub>TH</sub>

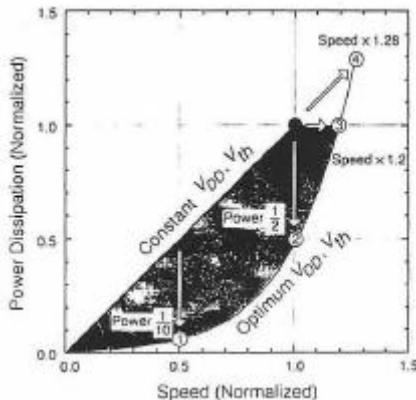

Fig. 2 Speed and power saving by optimum V<sub>DD</sub> and V<sub>TH</sub>

(1)式でわかるように、低電力回路実現のためには電源電圧を下げることが最も有効な方法である。しかし、応答速度の劣化の問題が起こる。ゲート遅延は以下の式で与えられる[6]。

$$t_{pd} = \frac{kC_L V_{DD}}{(V_{DD} - V_{TH})^a} \quad (2)$$

ここで、乗則モデルより  $a$  は約 1.3 であり、 $k$  は定数である。電源電圧  $V_{DD}$  のみを下げる回路スピードが減少してしまうので、しきい値電圧  $V_{TH}$  も下げなければならない。 $0.3\mu m$  デバイスパラメータを用いて(1),(2)式を計算した結果を Fig. 1[7]に示す。Fig. 1 より、一般に消費電力を減らすと遅延時間が増大することがわかる。しかし、遅延時間の等高線に沿って、 $V_{DD}$  と  $V_{TH}$  を共に下げれば、

遅延時間を増大させずに消費電力を削減できる。例えば図の A 点( $V_{DD}=3V$ ,  $V_{TH}=0.8V$ )から B 点( $V_{DD}=2V$ ,  $V_{TH}=0.4V$ )に  $V_{DD}$  と  $V_{TH}$  を同時に下げれば、回路遅延を増大させずに電力を半減できる。

しかし、 $V_{TH}$  を 0.1-0.2V 程度まで下げるリーケ電流が増大し(1)式において第2項が支配的になってくるので、リーケ電流も含めて消費電力が最小になるように  $V_{DD}$  と  $V_{TH}$  を最適化する必要がある。

リーケ電流による電力消費が全体の電力のおよそ 10% 程度になるように  $V_{DD}$  と  $V_{TH}$  を最適化した場合の、動作速度と消費電力の関係を図 Fig. 2[8]に示す。例えば、の条件で設計すると動作速度は半分になるが消費電力を 10 分の 1 にできる。の条件では動作速度を変えずに消費電力を半減できる。の条件では消費電力を変えずに動作速度を 1.2 倍にできる。このようにして  $V_{DD}$  と  $V_{TH}$  を最適化すると、一定の  $V_{DD}$  と  $V_{TH}$  で設計していた従来の場合に無駄になっていた消費電力を大きく改善することができる。

## 3. 低消費電力 SRAM

### 3.1 SRAM の低電圧化

プロセッサ内に組み込まれるメモリとしては、レジスタファイル、キャッシュ、および仮想記憶システムの高速化のためのアドレス変換バッファ(TLB: Translation-Lookaside Buffer)がある。これらのメモリは論理回路部分と同等の高速性を要求されるので通常 SRAM セルを用いる。SRAM の低消費電力化については多くの研究が成されている[9]。

メモリ部は主に SRAM 回路であり、セル内のノードにはデータが格納されている。もし、しきい値を落とせば、高負荷のビット線から MOS を通って流れるリーケ電流が発生し、最悪の場合データが失われるおそれもある。また、高負荷のワード線やビット線を充電するには、充分な電流を供給する必要があり、供給電圧を著しく下げるることは難しい。

メモリ部のセルは低電圧、高速性を要求されるので通常完全 CMOS セルを用いるが、データの書き込み、読み出しの操作を伴うので論理回路部分より低電圧化は難しい。データラッチ部のトランジスタは完全にデータをストアするために High-V<sub>TH</sub> MOS でなければならない。もし、Low-V<sub>TH</sub> MOS であるとプロセスによるしきい値ばらつきの結果、高負荷のビット線から MOS を通って流れるリーケ電流がラッチ部で発生し、消費電力がかえって増大する可能性がある。最悪の場合データが失われるおそれもある。また、通常、ビット線には多くのセルが接続されており負荷容量が大きく充分な電力供給能力を必要とするので蓄えられるデータやビット線充電に用いる電圧は高い

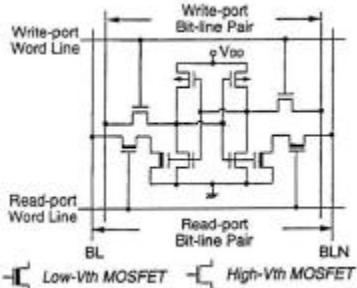

Fig. 3 The multi-Vth dual-port memory cell

電圧でなければならない。他にもワード線の駆動能力の問題などを考慮に入れると高速・低電圧の SRAM セルの実現は容易ではない。

### 3.2 SRAM セル低電圧化の例 [10]

低電圧 SRAM の実現が実際にどれだけ困難であるかについて、実際の例で述べてみる。以下に紹介するものは、MTCMOS/SIMOX 技術を用いた 0.5-1V 動作の SRAM セルである。セル回路図を Fig. 3 に示す。MTCMOS とは Multi Threshold CMOS の略で、高いしきい値の MOS と低いしきい値の MOS を適切に用いる消費電力の削減のための技術である。

データストア部と書き込み用のパストランジスタには High-V<sub>TH</sub> MOS( $V_{TH}=0.35V$ )が用いられ、読み出し用のトランジスタには Low-V<sub>TH</sub> MOS( $V_{TH}=0.15V$ )が用いられている。書き込み用と読み出し用のポートが分かれているのは、低電圧での読み出し誤りをなくすためである。Low-V<sub>TH</sub> MOS を用いているのでリーク電流を防ぐためにビット線は低くプリチャージされている。

このセルは  $V_{DD}=0.5V$  で動作することが確認されており低消費電力を実現しているが、遅延は  $V_{DD}=1.0V$  の場合の 5 倍もあり高速化には難がある。また、セル内には高いしきい値の MOS を用いているが、そのしきい値は 0.35V と低くプロセスのばらつきが原因でリーク電流が発生する心配もある。その他、MTCMOS のため設計プロセスはやや複雑になること、SOI テクノロジはまだ充分に普及しておらず誰もが簡単に扱うことのできるものではないことがあげられる。

### 3.3 低振幅書き込み方式 (Low-swing bit-lines)

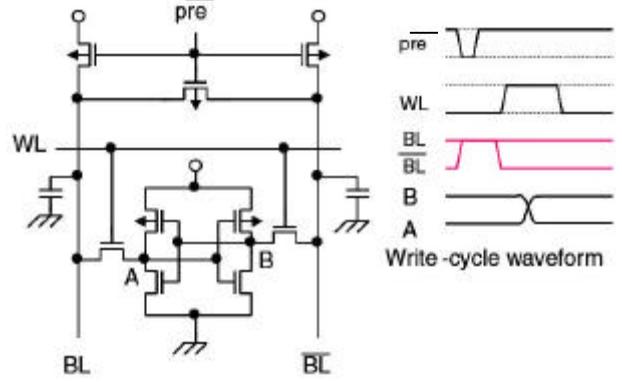

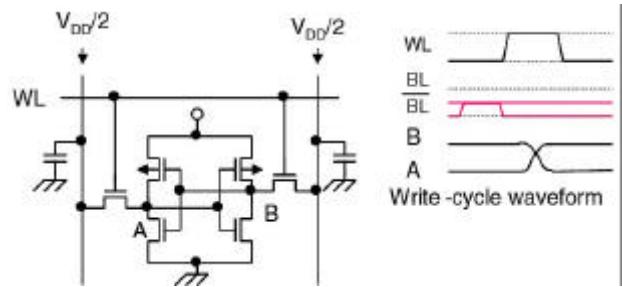

前節までで SRAM セルの低電圧化は困難であることを確認したので、別の観点から消費電力を削減する方法を考えてみる。従来の SRAM セルの回路図および書き込み動作の信号波形を Fig. 4 に示す。SRAM セルの書き込み動作について簡単に説明する。

書き込みを行う前にまず両方のビット線の電位を電源電圧  $V_{DD}$  まで引き上げる(プリチャージ)。次に書き込みたい

Fig. 4 Conventional SRAM memory cell and write operation

Fig. 5 Half-swing bit-lines SRAM memory cell and write operation

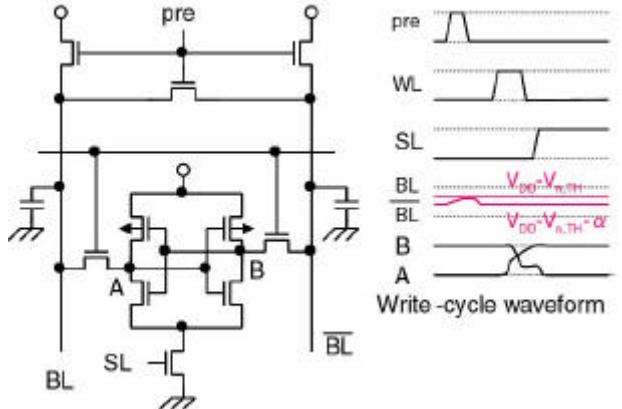

Fig. 6 Low-swing bit-lines SRAM memory cell and write operation

データに応じて片方のビット線の電位をグラウンド  $V_{SS}$  まで下げる。ワード線(WL)を開けると、ビット線は負荷容量が大きいのでセル内のノードが反転し新しいデータが書き込まれる。(ただし、書き込みたいデータがすでに記憶されているデータと同じ場合は反転しない。)

ここで問題なのは、負荷容量の大きいビット線をプリチャージする際に非常に大きな電力を消費することである。ビット線をフルスイングさせずに書き込みを行うことができれば消費電力を削減できる。そこでスタンフォード大の Mark A. Horowitz [11] らにより考え出された Half-swing 方式がある。その回路図および書き込み動作の信号波形を Fig.5 に示す。書き込む前にビット線を

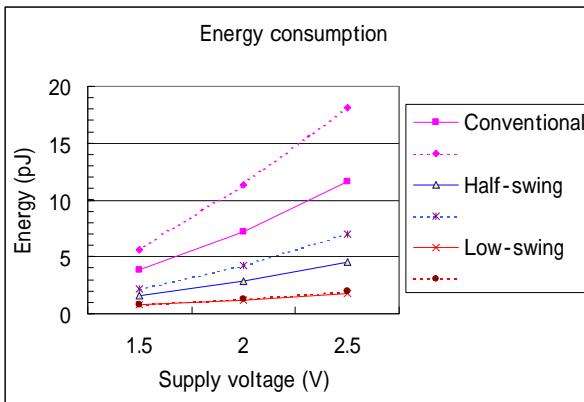

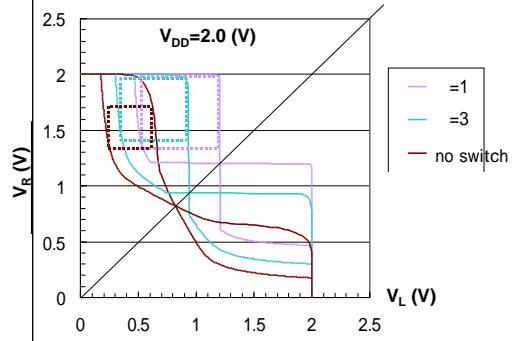

Fig. 7 Energy comparison of SRAM cells

Solid line: Write and read cycles

Dotted line: Write and write cycles

$V_{DD}/2$  にプリチャージしている点が従来の方式と異なっている。ハーフスイングであるため理論的には消費電力は半分になるはずである。しかし、この方法では問題点がある。まず、Half-swing 方式では書き込み時は  $V_{DD}/2$  にプリチャージして良いが、読み出しには  $V_{DD}/2$  にしておくと破壊読み出しになるおそれがあり、実際はビット線電位を  $V_{DD}/2$  以上にあげなければならならず消費電力はもっと大きくなる。また、スイングが  $V_{DD}/2$  でもまだ消費電力は大きくそれ以下に落とすことができない。

もし、ビット線を  $V_{SS}$  まで落とさずに、片方のビット線よりやや低いレベルに落とすだけで書き込みを行うことができたならば、次のプリチャージに要する消費電力を大幅に削減することが可能である。ただし、この場合ビット線間の電圧差が小さくセル内のノードを反転させるだけの駆動力がない。そこで、n MOS のスイッチを通常の SRAM セルの nMOS ドライバのソース側に付加することで低振幅書き込みを実現した。その回路図および書き込み動作の信号波形を Fig. 6 に示す。

書き込む前にまずプリチャージを行う。nMOS 負荷でプリチャージされるので、ビット線電位は  $V_{DD}-V_{TH}$  となる。次に片方のビット線の電位を  $V_{DD}-V_{TH-}$  まで下げる。

の値は  $0.15V \sim 0.30V$  くらいを想定している。ここでワード線(WL)を開けて書き込むのだが、ビット線間の振幅差が小さいとドライバの駆動力の方が強くノードの電位は反転しない。そこで、ドライバのソース側に付加した nMOS スイッチをあらかじめ切ってから、ワード線を開ける。すると、ノード電位はなれば浮いた状態になるので反転させることができる。反転が終わり二つのノード間の電位差が充分についたところでワード線を切り nMOS スイッチを開けると完全な反転が起こり書き込みが終了する。

この方法では、書き込みを終えたあとの次の動作でのプリチャージにかかる消費電力を大幅に削減できるので、書き込み読み出しの連続したサイクルで消費電力を削減できる。

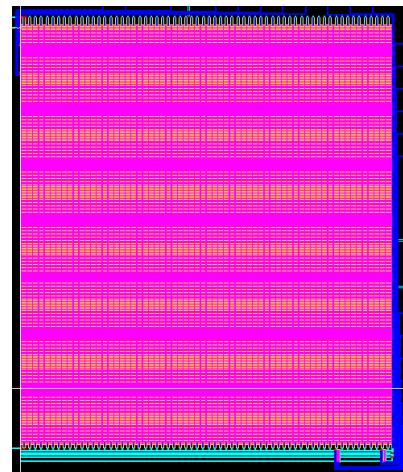

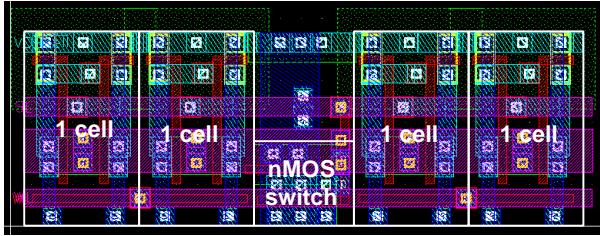

Fig. 8 Layout pattern of the SRAM cells

|                |                            |

|----------------|----------------------------|

| Technology     | 0.35μm CMOS 3-metal (Rohm) |

| Organization   | 256 × 256 cells            |

| Supply voltage | 1.5V ~ 2.5V                |

| Core size      | 4.0mm <sup>2</sup>         |

| Cell size      | 55.3μm <sup>2</sup>        |

Table 2 Features of the SRAM cells

きるという利点がある。また、プリチャージ時のビット線電位が  $V_{DD}-V_{TH}$  と  $V_{DD}/2$  以上であるために確実に読み出しを行うことができると予想される。

従来の SRAM セル及び Half-swing 方式、Low-swing 方式の消費電力の HSPICE シミュレーションを行った。その結果を Fig. 7 に示す。実線は書き込み読み出しサイクルにおけるエネルギー消費、点線は連続した書き込み書き込みサイクルにおけるエネルギー消費の量を示している。 $V_{DD}=1.5V$  における書き込み読み出しサイクルの消費電力は、Low-swing 方式の場合、従来の方式より 5 分の 1 に Half-swing 方式と比べても 2 分の 1 に削減されたことが確認された。書き込み書き込みサイクルでは、プリチャージの影響がじかにきてくるので、消費電力はさらに改善される。原理的には  $V_{DD}=1.5V$  以下でも動作が可能だが、今回試作に用いた Rohm の 0.35μm CMOS プロセスではしきい値が高くプリチャージ時のビット線電位が  $V_{DD}/2$  以下になってしまってシミュレーションは行っていない。

今回、考案した Low-swing bit-lines 方式のセルの試作を VDEC を通して行った。そのレイアウト図を Fig. 8 に概要を Table 2 に示す。今回はセル部のみの評価をすることが目的であるために、デコーダーやアドレスパッファ等の周辺回路は作成していない。また、読み出しの測定を確実に行えるようにするために、センサアンプをあえて入れず、パッファ出力としている。従来方式との消費電力の比較をするために、nMOS スイッチがついていない通常の

Fig. 9 Evaluation of read delay

Fig. 10 Simulation result of cell read delay

SRAM セルも TEG 中に入れてある。

なお、今回は  $V_{DD}-V_{TH-}$  の値を直接チップに与えるが、実際には回路内で発生させる必要があり、低消費電力で  $V_{DD}/2$  の電位を作り出す回路[12]などの検討が必要である

### 3.4 読み出し速度評価

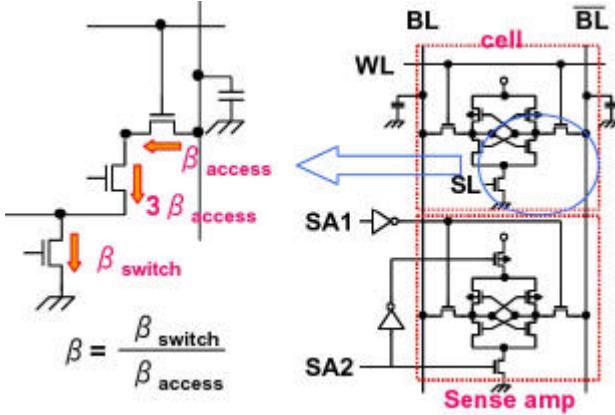

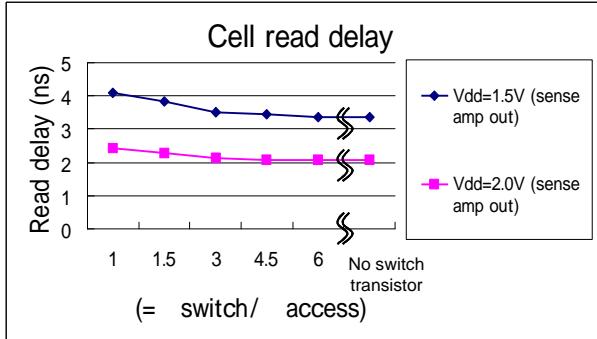

読み出しを行う際に、通常の SRAM セルではアクセストランジスタとドライバトランジスタの nMOS 二段で読み出しが、今回考案したセルは nMOS スイッチがついて三段で読みだすので、読み出しの遅延が増加することが予想された。そこで読み出し遅延の評価を行った。評価を行った際の回路図を Fig. 9 に示す。SRAM セルにセンスアンプをつけた回路で、ワード線を開いてからビット線間の電位差が 100mV 以上になり、さらにセンスアンプとビット線間のスイッチを切ってからセンスアンプ出力が  $0.1V_{DD}$  以下、 $0.9V_{DD}$  以上となるまでの時間を HSPICE シミュレーションで評価した。アクセストランジスタの導電係数  $\beta_{access}$  に対して、ドライバトランジスタの導電係数を  $3\beta_{access}$ 、nMOS スイッチの導電係数を  $\beta_{switch}$  とし、スイッチの導電係数のアクセストランジスタの導電係数に対する比 ( $= \beta_{switch} / \beta_{access}$ ) の値を変化させた。その結果を Fig. 10 に示す。

予想していたよりも読み出し遅延の増加は少なく、 $=3$  以上ではスイッチがない場合の読み出し遅延よりやや

Fig. 11 Analysis of static noise margin

Fig. 12 Simulation result of static noise margin

Fig. 13 Simulation result of Input/Output characteristics of inverter

大きさだけであった。そこで、今回の設計では  $=3$  として、読み出し遅延の増加は  $V_{DD}=1.5V$  でスイッチがない場合に比べて約 5% にとどまった。

### 3.5 ノイズマージン解析

読み出し時には、負荷容量の大きなビット線から電荷が流入してくるので、セル内の”0”が記憶されているノードの電位があがる。このあがり方が大きすぎる、すなわちノイズマージンが小さいとデータが失われるおそれがある。特に今回試作したセルは nMOS スイッチを付加したことによってドライブ能力が弱くなりセル内のノードの電位があがってデータを保てなくなることが心配されたので、

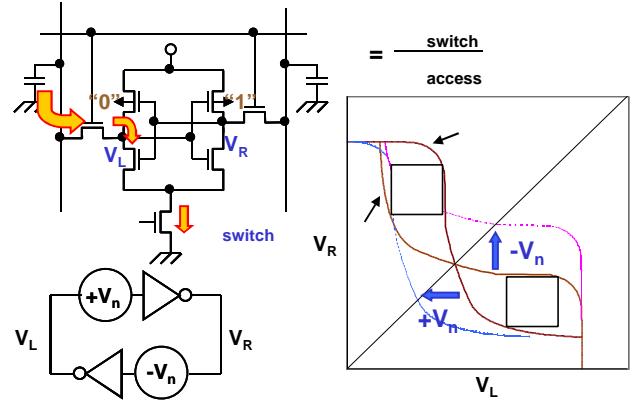

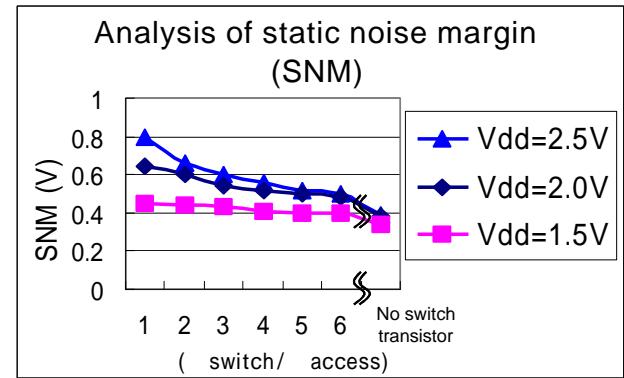

Fig. 14 Layout pattern of 4 SRAM cells

静的ノイズマージン(SNM)の解析を行った。SNMは次のように定義される [13] [14]。まず、Fig. 11においてインバータIとインバータOの入出力特性を同じ図に書き出す。二つの目ができるので、その中に入れることのできる最も対角辺の大きな正方形を書いたときのその正方形の辺の長さがSNMとして定義される。すなわち、セル内部のインバータを反転させない最大の電圧がSNMである。読み出し遅延の評価のときと同様に、スイッチの導電係数のアクセストランジスタの導電係数に対する比(=switch / access)の値を変化させた。その結果をFig. 12に示す。

予測に反してスイッチがある場合の方がSNMは大きく、さらにスイッチの導電係数が小さいほどSNMは大きくなかった。Fig. 13に $V_{DD}=2.0V$ でのインバータの入出力特性を示す。導電係数が小さい(=小さい)ほど確かにドライブ能力が弱くセル内のノード電位は引き上げられるが、一方で論理しきい値がかなり高い値にシフトしたことが、SNMが大きくなったことの原因であると考えられる。反転の付近ではカーブが非常に急峻で不連続であるが、この理由としては、nMOSスイッチをつけたために通常の解析とやや異なり今回は6つのトランジスタでノイズマージン解析を行っているので、フィードバックの影響からカーブが急峻になりノイズマージンが大きく見えるということが考えられる。

### 3.6 セルレイアウト

考案したSRAMセルの試作を行う際に最もネックになったものがセルのレイアウトである。4セル分のレイアウト図をFig. 14に示す。nMOSスイッチを付加したためにその分だけ回路面積が大幅に増大する。そこで、実際には4つのセルにつき1つのnMOSスイッチを付加することにし、4つのセルを同時に書き込みを行うようにした。通常のSRAMセルの6Tr部分は通常のレイアウトを行い4つのセルの中央にnMOSスイッチを配置し、同時に基盤コンタクトもとった。通常のSRAMセルのレイアウトに比べて約11%の面積増となった。(通常のSRAMセルでも4セルにつきいくつかの基盤コンタクトをうちセル間にやや隙間が空くので、それと比較したパーセンテージとした。)セル面積を極力抑えるためには、6Tr部分も含めて根本的なレイアウトの変更が要求されると考えられる。

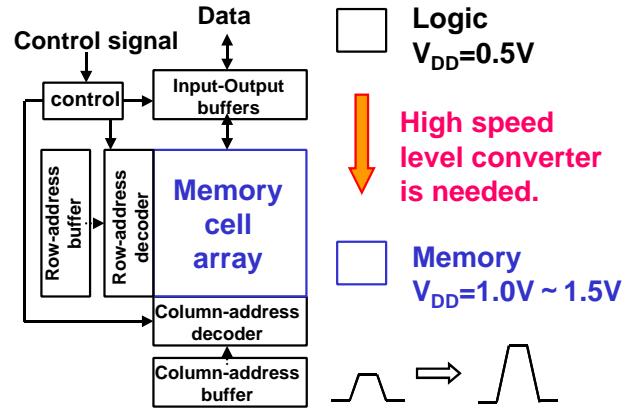

Fig. 15 An SRAM architecture

### 3.7 SRAM アーキテクチャ

前節までは考案した低振幅ビット線によるSRAMの書き込み方式について述べたが、次に、目指しているSRAMの全体像について触れる。SRAMのアーキテクチャをFig. 15に示す。今回、設計試作したチップはメモリセルアレイのみであったが、メモリはセルアレイのほかにロウおよびカラム方向のデコーダー、それぞれのアドレスバッファ、データの入出力バッファ、そしてこれらの制御回路が伴う。これらのアーキテクチャについては従来通りであり変更する予定はないが、消費電力の削減を図るために、デコーダー等の周辺回路は $V_{DD}=0.5V$ 程度の低い電源電圧で動作させ、メモリ部は $V_{DD}=1.0V\sim1.5V$ 程度のやや高い電源電圧で動作させることを考えている。すでに述べたようにメモリ部の低電圧化は難しいが、論理部の低電圧化はしきい値を落とすことによって可能であるからである。

しかし、ここで問題になるのは、低い電圧を高い電圧に変換するための高速かつ低消費電力なレベルコンバータを必要とすることである。高速SRAMを目指すにはロードコーダーの低電圧出力をできるだけ速く高い電圧に変換し、ワード線に入力しなければならない。また、書き込みが終わったら次の書き込みに備えてすみやかにワード線を切り、いくつかのワード線が同時に開いてしまうことのないようにしなければならない。

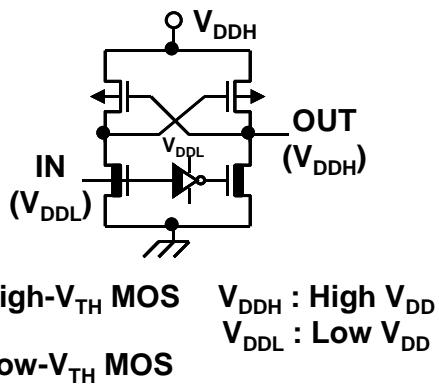

### 3.8 レベルコンバータ

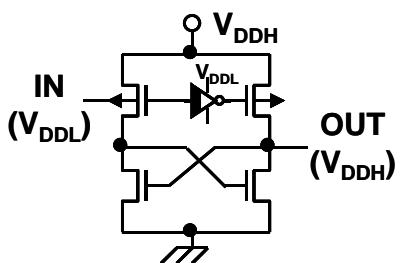

レベルコンバータに関する研究は多く行われており[15] [16]、特に消費電力の改善がいろいろとなされている。しかし、遅延の少ないレベルコンバータに関する研究は少なく、現在のところFig. 16のクロスカップル型のコンバータが遅延が少なくよく使用されている。ただし、これを $V_{DD}=0.5V$ 程度からのレベル変換に用いようとすると、そのままでは使用できず、nMOSを低いしきい値のMOSにする必要がある。また、pMOSもややしきい値を落とす必要がある。しきい値を落とさなくてもよい方法として、

Fig. 16 Conventional level converter

Fig. 17 pMOS type level converter

Fig. 18 Proposed level converter

Fig. 19 Proposed level converter

(Inverter type for word-line use only)

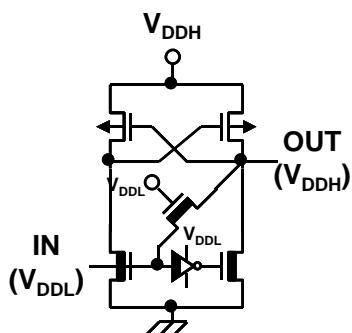

Fig. 17 のように pMOS で入力信号を受ける形式も考えられるが、この回路では pMOS を完全に切ることができず両方の pMOS が ON してしまい、多量の電流が流れる。電流パスをうまく切る方法を考えない限りこの方式は使用できない。

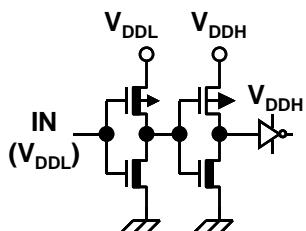

そこで、従来のクロスカップル型のレベルコンバータを検討し、Fig. 18 のような回路を考案した。低い電圧  $V_{DDL}=0.5V$  から高い電圧  $V_{DDH}=1.0V$  へ変換する HSPICE

シミュレーションを行った。従来の回路では立ち上がり遅延および立下り遅延とも約 1ns であったのに対して、考案した回路では立ち上がり遅延はほぼ同じであったが、立下り遅延が約 0.4ns と大幅に改善した。この理由は、入力と出力をむすぶ nMOS を付加したことによって、入力の”0”レベルの電位が出力を引っ張るからである。入力に”1”レベルの信号が来たときには、出力に対してやや押し込むが出力電位が上昇すると付加した nMOS は高い電圧を通せずに自動的に切れるので電流パスは生じない。

他に、消費電力を犠牲にしても変換速度が速くシンプルな回路として Fig. 19 のインバータを検討している。nMOS と pMOS のドライブ能力比を適切に設定することによって、立ち上がり遅延を約 0.6ns と高速にできる。ただし、立下り遅延はやや大きくなるが、適切な設計で約 1.2ns 程度に抑えられる。二段目の pMOS が完全に OFF せず消費電力が多いが、使用する場所を考えるとあまり問題にならない。なぜなら、このレベルコンバータはワード線を駆動するが、駆動されるワード線はたかだか 1 本であり残りのワード線は駆動されないからである。この回路方式は通常のレベルコンバータではなく、ワード線駆動のためのレベル変換のみに効力を発揮するものである。

以上、レベルコンバータについて述べたが、まだ検討は不十分であり以後も遅延、消費電力、面積等の観点から検討を続けていく予定である。

#### 4. まとめと今後の課題

現在、チップの高集積化・高性能化に伴ってチップの消費電力が急激に増大しており、特に携帯機器などにおいて消費電力の削減が緊急の課題となっている。中でも高速動作を要求されるプロセッサの消費電力の削減は急務である。そこで、プロセッサの消費電力を削減するための方法として、考案した SRAM セルの新しい書き込み方式を中心に述べた。

プロセッサは主に論理部とメモリ部よりなるが、論理部については電源電圧としきい値を共に落とすことで低消費電力化を図ることができる。しかし、メモリ部の電圧としきい値を落とすことは、リーク電流、負荷容量の大きなビット線の充電といった問題から容易ではない。

そこで、ビット線を低振幅で書き込みを行う方法を考案した。NMOS スイッチを通常の SRAM セルに付加するために、読み出し速度、ノイズマージン、レイアウト面積増でそれぞれの問題が生じたが、評価、工夫の結果、大きなデメリットにはならなかった。HSPICE シミュレーションの結果、 $V_{DD}=1.5V$  時における書き込み読み出しサイクルの消費電力が従来の約 5 分の 1 に削減されることが確認された。VDEC を通して実際にメモリセル部のみのチップを試作した。

メモリの全体像としては、デコーダー等の論理部は

$V_{DD}=0.5V$  程度の低電圧で、メモリ部は  $V_{DD}=1.0V\sim1.5V$  程度のやや高い電源電圧で動作させることを考えている。この場合、低い電圧を高い電圧に高速かつ低消費電力で変換するためのレベルコンバータが必要になる。そこで、高速なレベルコンバータの検討をしていくつかの回路方式を考案したが、まだ検討段階である。

今後の課題としては、設計および測定の二つにわけられる。設計については、まずセルのレイアウトをさらに工夫し面積増を抑える、高速・低消費電力のレベルコンバータを考案するという課題がある。さらに、次回の設計ではメモリ全体の設計を目指すので、デコーダー、パッファ等の設計がある。これと平行して、試作したチップの測定を行う。まず、実際に回路が所望の動作をするかを確かめた後に、速度、消費電力の評価を通常の SRAM セルと比較することで行う。最終的には  $0.5V, 1GHz$  で動作するプロセッサ内のメモリを目指す。

## Reference

- [1] F. Federico, H. Marcian. E Jr., M. Stanley, S. Masatoshi, "History of the 4004", IEEE Micro., Vol.16, No.6, pp.10-20. Dec., 1996

- [2] "International Technology Roadmap for Semiconductors 1999 edition", Semiconductor Industry Association

- [3] Hiroshi iwai, "CMOS Technology – Year 2010 and Beyond", IEEE J. Solid-State Circuits, vol.34, No.3, pp.357-366, Mar., 1999

- [4] "Mobile Pentium III Processor in BGA2 and Micro-PGA2 Packages Datasheet", <http://www.intel.com/>

- [5] "Mobile Power Guidelines Rev. 1.00", <http://www.intel.com/>

- [6] T. Sakurai and A.R. Newton, "Alpha-power law MOSFET model and its application to CMOS inverter delay and other formulas", IEEE J. Solid-State Circuits, vol.25, No.2, pp.584-594, Apr., 1990

- [7] T. Kuroda and T. Sakurai, "Overview of low-power ULSI circuit techniques", IEICE Trans. on Electronics, E78-C, Vol.4, pp.334-344, Apr., 1995

- [8] T. Kuroda and T. Sakurai, "Low-Voltage Technologies and Circuits", IEEE press, Low-Power CMOS Design, pp.61-65

- [9] B.S. Amrutur and M.A. Horowitz, "Speed and power Scaling of SRAM's", IEEE J. Solid-State Circuits, vol.35, No.2, pp.175-185, Feb., 2000

- [10] T. Douseki, N. Shibata and J. Yamada, "A 0.5-1V MTCMOS/SIMOX SRAM Macro with Multi-Vth Memory Cells", IEEE International SOI Conference, 2000

- [11] Kenneth W. Mai, Toshihiko Mori, Bharadwaj S. Amrutur, Ron Ho, Bennett Wilburn, Mark, A. Horowitz, Isao Fukushi, Tetsuo Izawa, and Shin Mitarai, "Low-Power SRAM Design Using Half-Swing Pulse-Mode Techniques", IEEE J. Solid-State Circuits, vol.33, No.11, pp.1659-1671, Nov., 1998

- [12] Syuso Fujii, Shozo Saito, Yoshio Okada, Masayuki Sato, Shizuo Sawada, Satoshi Shinozaki, Kenji Natori, Osamu Ozawa, "A 50- $\mu$ A Standby 1M  $\times$  1/256K  $\times$  4CMOS DRAM with High-Speed Sense Amplifier", IEEE Journal of Solid-State Circuits, Vol. 21, No. 5, Oct., 1986

- [13] Evert Seevinck, Frans J. List, and Jan Lohstroh, "Static-Noise Margin Analysis of MOS SRAM Cells", IEEE J. Solid-State Circuits, vol.22, No.5, pp.748-754, Oct., 1987

- [14] Azeez J. Bhacnagarwala, Xinghai Tang, James D. Meindl, "The Impact of Intrinsic Device Fluctuations on CMOS SRAM Cell Stability", IEEE J. Solid-State Circuits, vol.36, No.4, pp.658-665, Apr., 2001

- [15] Yusuke Kanno, Hiroyuki Mizuno, Kazuo Tanaka, and Takao Watanabe, "Level Converters with High Immunity to Power-Supply Bouncing for High-Speed Sun-1-V LSIs", Symposium on VLSI Circuits Digest of Technical Papers, pp.202-203, 2000

- [16] Hui Zhang, Jan Rabaey, "Low-Swing Interconnect Interface Circuits", International Symposium on Low Power Electronics and Design, pp.161-166, 1998