# 0.5V VLSI Processor Circuit Technologies

## 0.5V VLSI プロセッサ回路技術

電子工学専攻 桜井研究室

修士1年 06435 服部 貞昭

### Abstract

LSI techniques have advanced remarkably during past 30 years and are expected to continue to progress more and more. But an increase of power dissipation has become one of the most significant problems. Lowering the supply voltage ( $V_{DD}$ ) is the most effective way to achieve low-power application. However, the performance is degraded drastically. One solution is to decrease the threshold voltage ( $V_{TH}$ ). But reducing  $V_{TH}$  cause a significant increase of leakage current. Optimization of both  $V_{DD}$  and  $V_{TH}$  is needed. Many studies of low-voltage and low  $V_{TH}$  application are reported.

In this paper, some kinds of low-voltage CMOS LSI technologies, such as MTCMOS, VTCMOS, SCCMOS, Dual- $V_{TH}$ , Dual- $V_{DD}$  and Variable Supply scheme are reported. And low voltage SRAM memory cells are discussed.

### 1. はじめに

1971年にインテルにより初めて作られたマイクロプロセッサ Intel4004 は、 $10\mu$  テクノロジでわずか 2,300 個のトランジスタから成るクロック周波数 740KHz のチップであった[1]。それ以来、LSI 技術は劇的な進歩を遂げ、現在では数百万個のトランジスタを積んだクロック周波数 1GHz を超えるチップが製造されるに至っている。そして、ITRS (International Technology for Semiconductors)[2]によれば、LSI 技術の進歩は今後 10 年間も同じ勢いで続くと予想されており、Table 1 に示すように 2011 年には、約 0.5V で 10GHz を超えるチップが登場する可能性がある。

| Year         | 1999 | 2002 | 2005 | 2008 | 2011 | 2014 |

|--------------|------|------|------|------|------|------|

| Tech.(nm)    | 180  | 130  | 100  | 70   | 50   | 35   |

| Lg(nm)       | 140  | 100  | 70   | 50   | 30   | 20   |

| $V_{dd}$ (V) | 1.5  | 1.2  | 0.9  | 0.6  | 0.5  | 0.3  |

| Freq.(GHz)   | 1.25 | 2.1  | 3.5  | 6.0  | 10.0 | 13.5 |

| Power(W)     | 90   | 130  | 160  | 170  | 174  | 183  |

Tech.: Technology Node, Lg: Gate Length of microprocessor,

$V_{dd}$ : Minimum logic  $V_{dd}$  for lowest power,

Freq.: Frequency, Power: High-performance with heatsink

Table 1 ITRS Road Map

しかし、Technology Node が 100nm より小さい領域の

デバイス実現には相当な困難が伴うと予測されている[3]。また周波数の増加、回路規模の増加に伴ってチップあたりの消費電力が増加する傾向にあり、消費電力に対して何の対策も施さなければ 200W 近くになることが予想される。特にポータブル機器においては電力の削減が緊急の課題となっている。例えば、600MHz の Mobile Pentium コアの最大消費電力は 21.6W[4]であり、フルサイズのノート PC の消費電力ガイドラインである 12W (プロセッサと 2 次キャッシュの最大消費電力) [5]をすでに超えている。

このような消費電力の増大の問題を解消すべく、近年では、ある程度速度を犠牲にしても消費電力が小さいプロセッサの研究が盛んに行われるようになりつつある。今年 1 月にはトランスマタより低消費電力プロセッサ Crusoe が開発された。これは X86 命令を VLIW 命令に変換する Code Morphing[6]技術および、必要なパフォーマンスに応じて電源電圧と周波数を動的に制御する LongRun 技術を使用して、消費電力を数 W オーダに減少させた画期的なプロセッサである。今後さらに周波数が増大することを考えると、低消費電力への要求はますます高まっていくと思われる。そこで、本輪講では、回路技術に焦点を絞って低消費電力の実現法について述べる。

現在のプロセッサで用いられている回路形式の多くは CMOS 回路であり、デジタル CMOS 回路の消費電力の削減に関しては様々な観点から多くの研究がなされている[7][8]。デジタル CMOS 回路の消費電力は次のような式で与えられる。

$$P = p_t f_{CLK} C_L V_S V_{DD} + I_0 10^{-(V_{TH}/S)} V_{DD} \quad (1)$$

ここで、 $p_t$  はスイッチング確率、 $f_{CLK}$  はクロック周波数、 $C_L$  は負荷容量、 $V_S$  は信号振幅、 $V_{DD}$  は電源電圧、 $I_0$  はチップ内全トランジスタの合計幅に比例する定数、 $S$  はサブスレッショルド係数である。第 1 項は負荷の充放電に要する電力であり、第 2 項はリーク電流による消費電力である。通常の CMOS では第 1 項の動作電流の方が支配的である。

まず、スイッチング確率  $p_t$  を減少させる方法がある。データ表現形式を変更して bit の反転を少なくしたり[9]、あるいは、使用されていないモジュールへの電力供給を自動的にシャットダウンする[10]。次に、クロック周波数  $f_{CLK}$  の低減については、高速性を必要としない部分の周波数を通常の周波数の 2 分の 1、4 分の 1 などに下げるという方法がある[11]。負荷容量  $C_L$  の低減については、プロセス技術の進歩によるところが大きいが、パストランジスタ論理回路を用いてトランジスタ数、配線数を少なくすることにより低減を図る方法もある[12]。

そして、低電力を実現するために最も効果的な方法は電源電圧を減少させることである。なぜなら通常の回路では

信号振幅は電源電圧に等しく、電力は電源電圧の2乗に比例しているからである。しかし、電源電圧を落とせば回路の遅延が増加するという問題が起こる。そこで、しきい値を変えることにより、遅延やリーク電流の制御をする。

2章では、低電圧化において重要である、電圧およびしきい値の、遅延および消費電力との関係について触れる。3章では論理回路部の低電圧技術について触れる。また、プロセッサの低消費電力化のためにはキャッシュ、レジスタファイル等のメモリ部も低電圧化する必要があるのでそれについて4章で簡単に触れる。

## 2. 低電圧、低しきい値電圧での設計

(1)式でわかるように、低電力回路実現のためには電源電圧を下げることが最も有効な方法である。しかし、応答速度の劣化の問題が起こる。ゲート遅延は以下の式で与えられる[13]。

$$t_{pd} = \frac{kC_L V_{DD}}{(V_{DD} - V_{TH})^a} \quad (2)$$

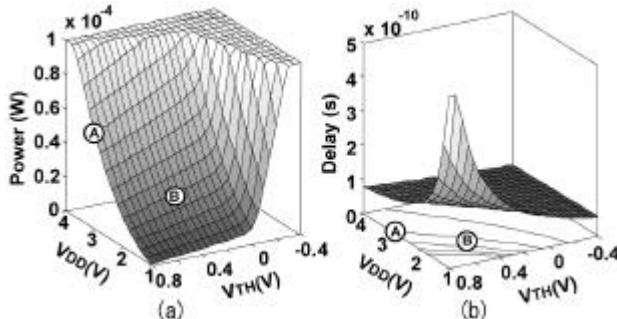

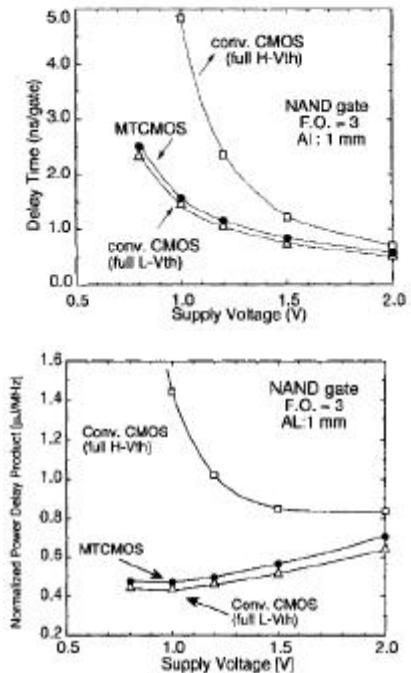

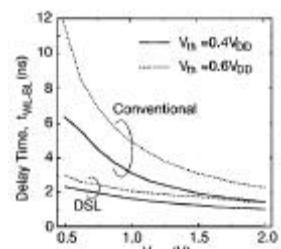

ここで、乗則モデルより  $a$  は約 1.3 であり、 $k$  は定数である。電源電圧  $V_{DD}$  のみを下げる回路スピードが減少してしまうので、しきい値電圧  $V_{TH}$  も下げるなければならない。 $0.3\mu\text{m}$  デバイスパラメータを用いて(1),(2)式を計算した結果を Fig. 1[14]に示す。

Fig. 1 (a) Power Dependence on  $V_{DD}$  and  $V_{TH}$  (b) Delay Dependence on  $V_{DD}$  and  $V_{TH}$

Fig. 1より、一般に消費電力を減らすと遅延時間が増大することがわかる。しかし、遅延時間の等高線に沿って、 $V_{DD}$  と  $V_{TH}$  を共に下げれば、遅延時間を増大させずに消費電力を削減できる。例えば図の A 点( $V_{DD}=3\text{V}$ ,  $V_{TH}=0.8\text{V}$ )から B 点( $V_{DD}=2\text{V}$ ,  $V_{TH}=0.4\text{V}$ )に  $V_{DD}$  と  $V_{TH}$  を同時に下げれば、回路遅延を増大させずに電力を半減できる。

しかし、 $V_{TH}$  を 0.1-0.2V 程度まで下げるリーキ電流が増大し(1)式において第2項が支配的になってくるので、リーキ電流も含めて消費電力が最小になるように  $V_{DD}$  と  $V_{TH}$  を最適化する必要がある。

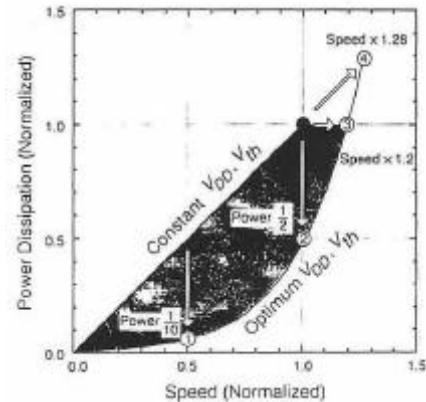

リーキ電流による電力消費が全体の電力のおよそ 10% 程度になるように  $V_{DD}$  と  $V_{TH}$  を最適化した場合の、動作速度と消費電力の関係を図 Fig. 2[15]に示す。例えば、の条件で設計すると動作速度は半分になるが消費電力を 10 分の 1 にできる。の条件では動作速度を変えずに消費電力を半減できる。の条件では消費電力を変えずに動作速度を 1.2 倍にできる。このようにして  $V_{DD}$  と  $V_{TH}$  を

最適化すると、一定の  $V_{DD}$  と  $V_{TH}$  で設計していた従来の場合に無駄になっていた消費電力を大きく改善することができる。

Fig. 2 Speed and Power Saving by optimum  $V_{DD}$  and  $V_{TH}$

だが、ここで一つ大きな問題がある。それは、プロセスに起因するしきい値電圧のばらつきである。 $V_{DD}$  を下げるに  $V_{TH}$  のばらつきを小さくしない限り動作速度は大きくばらつく。しきい値電圧が  $V_{TH}$  ばらついたときの遅延時間のばらつき  $T_{pd}$  は(2)式より次のように求まる。

$$\frac{\Delta T_{pd}}{T_{pd}} = \frac{a \Delta V_{TH}}{V_{DD} - V_{TH}} \quad (3)$$

$V_{DD}$ 、 $V_{TH}$  をそれぞれ  $V_{DD}$ 、 $V_{TH}$  に下げたときの動作速度が  $n$  倍になるとしたとき遅延時間のばらつきが変わらないようにするために(2),(3)式より

$$\frac{\Delta V_{TH}'}{\Delta V_{TH}} = \left( \frac{V_{DD}'}{V_{DD}} \right)^{1/a} \quad (4)$$

となる。例えば  $V_{DD}=3\text{V}$ ,  $V_{TH}=0.8\text{V}$  を  $V_{DD}=1.0\text{V}$ ,  $V_{TH}=0.3\text{V}$  まで下げたとすると(2)式より動作速度は半分になるので、動作速度のばらつき割合が従来と変わらないためには、 $V_{TH}$  のばらつきの割合は(4)式より 0.23 倍に小さくしなければならない。しかし、 $V_{TH}$  のばらつきを 4 分の 1 に抑えることは非常に困難である。

また、低しきい値電圧の別の問題として、低しきい値でのリーク電流の急激な増加がある。スタンバイ電力が増大するので、特に携帯機器にとっては重大な問題である。また、不良に起因するリーク電流が正常なトランジスタの増大したリーク電流に埋もれて判別できなくなり、製品出荷時のテスト工程の一つであるスタティック電流検査(IDDQ テスト: Quiescent Current Testing)ができなくなる。その結果、テストコストが高くなったり、市場不良の危険性も高まる。

しかしながら消費電力の削減という緊急の課題を考えるとしきい値を落として電源電圧を下げる必要がある。デバイス的な観点でも、MOS の微細化が進むと高電圧ではドレイン近傍で生じたホットエレクトロンが酸化膜にトラップされ、高周波回路ではしきい値の劣化の原因になる[16]ので印加電圧は小さい方が良い。

ただ、回路によっては高電圧を必要とする部分もありう

るので、回路ごとに異なる電源電圧を供給する場合もある。電源電圧の異なるチップ間で相互に信号をやりとりするためには、入出力回路に工夫を要する。また、最適な電源電圧は一般にチップ毎に異なるので、その数だけの外部電圧を用意しなければならない。この問題の解決法として、電源電圧変換回路の研究も行われている。

### 3. 論理回路部の低電圧技術

第2章で述べたように消費電力を減少させるためには、電源電圧  $V_{DD}$  としきい値  $V_{TH}$  を適切に制御して落としていかなければならない。これらの制御には Table2 に示すように様々な方法がある。

|                   | Active Power    | Standby Power             |

|-------------------|-----------------|---------------------------|

| Multiple $V_{TH}$ | Dual- $V_{TH}$  | MTCMOS<br>SCCMOS<br>BGMOS |

| Variable $V_{TH}$ | VTCMOS          | VTCMOS                    |

| Multiple $V_{DD}$ | Dual- $V_{DD}$  | (SCCMOS)<br>(BGMOS)       |

| Variable $V_{DD}$ | Variable Supply |                           |

Table 2 Controlling  $V_{DD}$  and  $V_{TH}$  for low power

Table2 は上から  $V_{TH}$  を複数(通常 2 個)用いる方法、 $V_{TH}$  を可変制御する方法、 $V_{DD}$  を複数(通常 2 個)用いる方法、 $V_{DD}$  を可変制御する方法であり、それぞれに動作時の電力を減少させるための技術およびスタンバイ時の電力を減少させるための技術がある。

#### 3.1 しきい値制御

##### 3.1.1 MTCMOS (Multiple Threshold-Voltage CMOS)

[17]

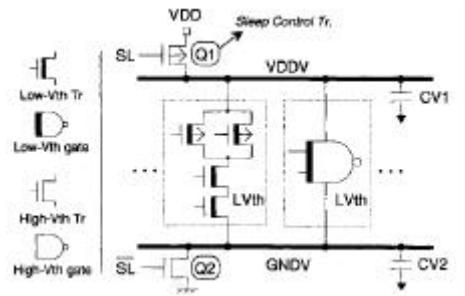

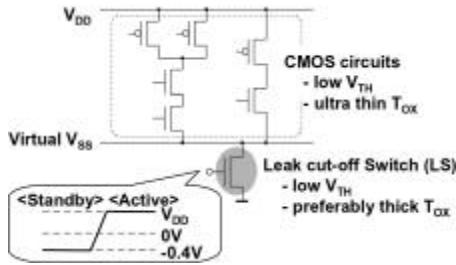

MTCMOS 回路は高いしきい値(High- $V_{TH}$ )の MOS と低いしきい値(Low- $V_{TH}$ )の MOS とから構成される CMOS 回路である。0.5  $\mu m$  デバイスでは、High- $V_{TH}$  が 0.6V、Low- $V_{TH}$  が 0.3V 程度である。基本的な MTCMOS 回路を Fig. 3 に示す。点線内の論理回路部分は Low- $V_{TH}$  MOS で構成されており、仮想電源線である VDDV と GNDV に接続されている。実電源線と仮想電源線は、High- $V_{TH}$  MOS の Q1, Q2 によって接続されており、これらのトランジスタは、アクティブモードとスリープモードの切り替えを行う信号 SL によって制御され、リーク電流を防ぐ役目を果たす。

簡単に動作を示すと、まず通常動作のアクティブモードでは、パワースイッチ Q1, Q2 が ON し仮想電源線 VDDV と GNDV は電源線として働く。CMOS 論理回路は Low- $V_{TH}$  MOS で構成されているので、1V 以下の低電圧でも高速に動作する。一方、待機時のスリープモードでは、High- $V_{TH}$  である Q1, Q2 が OFF しリーク電流パスを完全に遮断するので、論理回路部分が Low- $V_{TH}$  MOS で構成されているにもかかわらず、スタンバイ電流を 3 枠から 4 枠下げることができる。

Fig. 3 MTCMOS circuit scheme

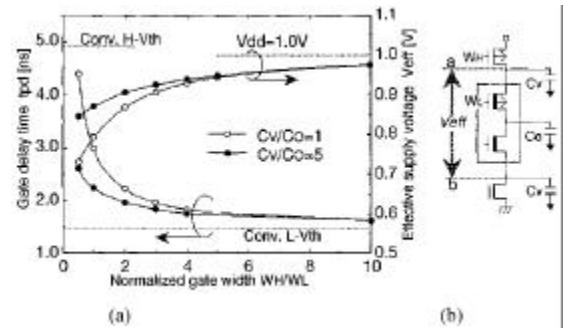

Fig. 4 The effect of power switch transistor size and capacitance of virtual power line (a) Simulation results

(b) Circuit model

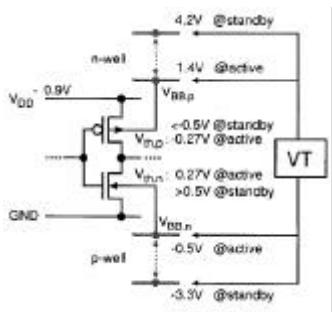

Fig. 5 MTCMOS performances (a) Gate delay time (b) Normalized power delay product

MTCMOS 回路の速度性能はパワースイッチ Q1, Q2 のゲート幅と仮想電源線の容量  $C_{V1}$ ,  $C_{V2}$  の二つの要因で決まる。Q1, Q2 のゲート幅が大きいほど ON 抵抗が小さくなり大きな電流供給能力を持つ。また、 $C_{V1}$ ,  $C_{V2}$  が大きいほど仮想電源線の電圧降下による速度劣化を抑えられる。

これらの影響のシミュレーション結果を Fig. 4 に示す。

(a)は正規化されたゲート幅  $W_H/W_L$  に対するゲート遅延時間と論理回路の有効動作電圧  $V_{eff}$  を示している。 $V_{eff}$  は  $V_{DDV}$  と  $GNDV$  間の瞬時最低電圧として定義されている。(b)はシミュレーションに用いた回路図である。パワースイッチのゲート幅と仮想電源線の容量の両方が大きいほど速度性能も有効動作電圧も改善されている。

Fig. 5 にMTCMOSによるNAND回路の速度、消費電力特性を示す。従来のHigh- $V_{TH}$  CMOS回路に比べ、電源電圧1Vでの遅延時間は約70%削減され、Low- $V_{TH}$  CMOSと同等の速度性能が得られている。エネルギー遅延積はHigh- $V_{TH}$  CMOS回路に比べて非常に小さくなっている。また、図には示していないがリーク電流は50nA以下に抑えられている。

欠点としては、パワースイッチに充分な電流供給能力を持つたためにゲート幅の大きいMOSを挿入しなければならず、また待機時でもデータを保持する特殊なラッチ回路[18]が必要なため面積ペナルティが大きいこと、 $V_{TH}$ のばらつきの影響を受けること、 $V_{DD}$ が非常に低くなると充分な有効動作電圧が供給できなくなることなどがあげられる。

### 3.1.2 VTCMOS (Variable Threshold-Voltage CMOS)[19]

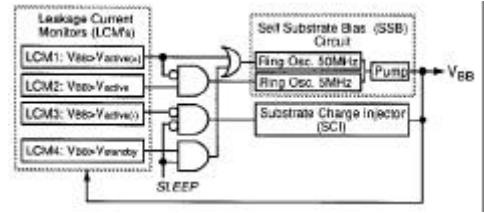

VTCMOS回路をFig. 6に示す。トランジスタのしきい値は基板バイアス制御により変更可能である。アクティブモードではしきい値を低くすることによって高速動作を可能にし、スタンバイモードではしきい値を高くしてリーク電流をカットする。

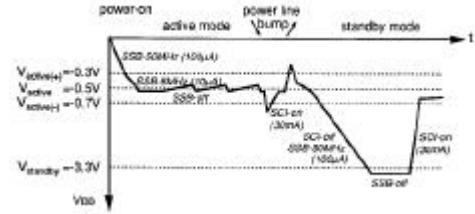

VTCMOSの基板バイアス制御回路の一例をFig. 7に示す。LCM(Leakage Current Monitor)はリーク電流のモニタ回路であり、リーク電流の大きさに応じて、基板電位発生回路(SSB; self-substrate bias circuit)と基板電荷注入回路SCI(SCI; substrate charge injector)をFig. 8に示すように制御して基板電位 $V_{BB}$ を変更する。目標とする動作時の基板電位 $V_{active}$ の前後に二つの基準電位 $V_{active(+)}$ と $V_{active(-)}$ を設定することで、 $V_{BB}$ が目標の $V_{active}$ から大きくかけ離れたときの回復を早くし、また $V_{active}$ 周辺での制御性を高くしている。 $V_{active}$ に近づくとSSBの電流駆動能力を下げて目標を大きく越えないようにしている。スタンバイモードからアクティブモードまでの復帰時間は0.1μsである。スタンバイ時のリーク電流は10nAのオーダに抑えられている。

Fig. 6 VTCMOS circuit scheme

Fig. 7 VT block diagram

Fig. 8 Substrate bias control in VT

VTCMOSの最大の特徴はトランジスタを4端子デバイスとして用いることにより、従来はデバイスの製造条件で決まっていたしきい値 $V_{TH}$ を自由に制御できるようにしたことである。リーク電流を設定値に等しくなるように制御することで $V_{TH}$ のばらつきを補償できる。

欠点としては、基板制御回路が必要なために制御回路が複雑になること、スタンバイ時も回路の制御が必要になるので、ある程度の電力が必要であること、バイアス制御回路にTriple well構造のMOSが必要なこと、基盤バイアスによるpn接合面でのリークなどがあげられる。

### 3.1.3 SCCMOS (Super Cut-Off CMOS) [20]

以上で紹介したMTCMOSとVTCMOSがMOSの低電圧化のための従来からの主要な手法だが非常に低い電圧ではそのままでは適用できない可能性がある。 $V_{DD}$ が0.5V程度の領域に入ると、高速な応答を得るためにLow- $V_{TH}$ を0.1-0.2V程度まで下げなければならない。しかし、しきい値が非常に低い場合スタンバイ時のリーク電流が大きくなる。かといって、 $V_{DD}$ が低いと電力供給能力の問題から、MTCMOSのようにHigh- $V_{TH}$ を直列挿入できない。そこで考え出されたのがSCCMOSである。Fig. 9に回路図を示す。

Low- $V_{TH}$ の電流カットオフnMOSが挿入されているのでアクティブ時には高速で動作する。スタンバイ時には、カットオフnMOSのゲートに負電圧-0.4Vをかけることによりリーク電流を1pAのオーダまでカットする。通常の回路と同様に作製できるので、SOIやパストランジスタにも応用できる。しかし、スタンバイ時には論理回路部分におけるデータが失われるので、MTCMOSのようにラッチ回路を入れる必要がある。

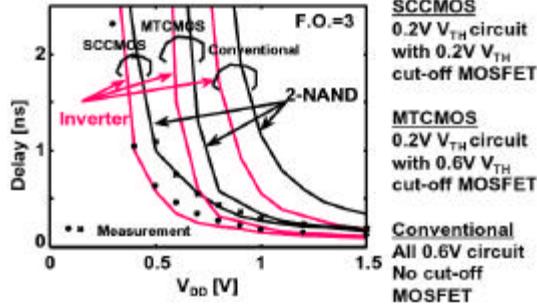

Fig. 10に従来の高いしきい値だけで構成されるCMOSおよびMTCMOS、SCCMOSの遅延を2NANDとインバータで比較した結果を示す。どちらの場合も、従来のCMOSよりもMTCMOSの方が遅延が少なく、さらにSCCMOSが最も遅延が遅延が少ないことがわかる。特に $V_{DD}$ が小さくなるほどその傾向は顕著になる。

Fig. 9 SCCMOS circuit scheme

Fig. 10 Delay characteristics

### 3.1.4 BGMOS (Boosted Gate MOS) [21]

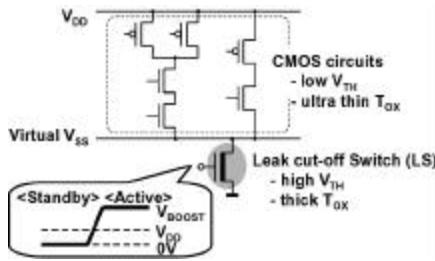

MTCMOS はカットオフスイッチの電流供給能力を大きくしなければいけないので面積ペナルティが大きい。また、VTCMOS は基板バイアスを印加してしきい値を制御する方式であったが、MOS の微細化が進むとゲートトンネルリーケ電流の増加、基板バイアス印加による pn 接合リーケ電流の増加といったデバイス面の問題も浮上してくる。そこで考えだされたのが BGMOS である。回路図を Fig. 11 に示す。

Fig. 11 BGMOS circuit scheme

論理回路部分は Low- $V_{TH}$  で非常に薄い酸化膜の MOS で構成されるのに対し、カットオフ nMOS は High- $V_{TH}$  で厚い酸化膜の MOS が使用されており、スタンバイ時にはサブスレッショルドリーケ電流とゲートリーケ電流の両方をカットする。アクティブ時にはカットオフ nMOS に  $V_{DD}$  より高い電圧をかけることにより、MTCMOS のように MOS のゲート幅を大きくすることなく高速な駆動を可能にする。図には示していないが、ゲート長 50nm の場合において従来の MTCMOS より、消費電力は 4 衍程度の削減でき面積も 2 分の 1 強にとどまる。

### 3.1.5 Dual-Threshold Voltage technique [22]

論理回路中の信号経路(パス)には、タイミングに余裕の

ないクリティカルパスとタイミングに余裕のあるノン・クリティカルパスが存在する。そこで、クリティカルパスには Low- $V_{TH}$  MOS を使用して高速化を図り、ノン・クリティカルパスには High- $V_{TH}$  MOS を使用してリーク電流を減少させる手法である。ほとんどのパスはノン・クリティカルであるので、Low- $V_{TH}$  MOS を使用する個所は少なく抑えられ消費電力も抑えられる。この発展形として、3種類のしきい値電圧の異なる MOS をそれぞれ適切な個所に配置して高速化・低消費電力化を図る研究もある[23]。

## 3.2 電源制御

### 3.2.1 多電源方式

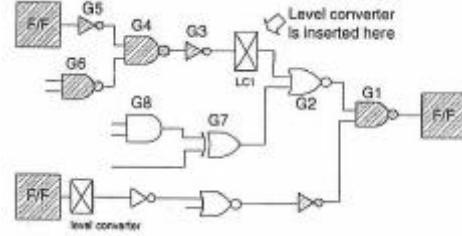

Fig. 12 Extended Clustered-Voltage-Scaling structure (VDDL gates are indicated as shaded.)

高電圧  $V_{DDH}$  と低電圧  $V_{DDL}$  を用意し、クリティカルパスには  $V_{DDH}$  をノン・クリティカルパスには  $V_{DDL}$  を電源電圧として用いる。Clustered-Voltage-Scaling[24]と呼ばれるその構造を Fig. 12 に示す。

二つの電源電圧を変換するレベルコンバータの数が最小になるように回路が自動生成される。詳細は省略するが、消費電力を半減させている。ただし、動作速度の速いレベルコンバータが必要である。

### 3.2.2 可変電源方式

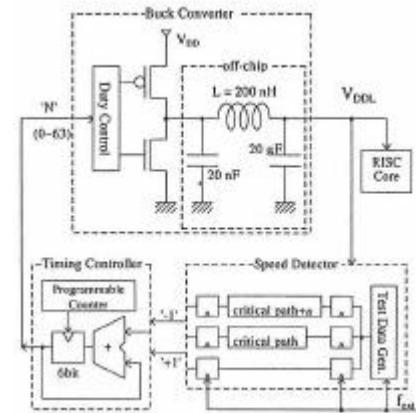

ボード設計との兼ね合いから電源電圧を容易に下げることができない場合には、DC-DC コンバータを用いて電圧を変換する。その一例である VS(Variable Supply-Voltage)方式[25]を Fig. 13 に示す。電源電圧を用いて外部電圧を降圧し、与えられた動作周波数に応じて、回路が動作する必要最小限の内部電圧を自動生成する方式である。

Fig. 13 VS scheme

動作速度検出回路にはクリティカルパスのレプリカが内蔵されており、このクリティカルパスの遅延とクロック

サイクルを比較する。例えばもしクロックサイクルより遅延が大きければ 1 を出力する。それを受けたコントローラは  $N(0\text{-}63)$  の値を増やして DC-DC コンバータに送る。すると DC-DC コンバータで外部電圧を変換し、さきほどより高い電圧を供給することにより遅延を少なくする。

VTCMOS 技術と併用することによって、30MHz における RISC プロセッサの消費電力を半減させている。最初に紹介した Crusoe プロセッサでも似たような方式が用いられている。

### 3.3 小振幅技术

通常、バスの信号振幅は電源電圧と同じだが、信号振幅を下げることにより負荷の充放電に要する消費電力を削減することができる。バスの小振幅化技術についてはいくつかの手法が提案されているが、主要なものを紹介する。

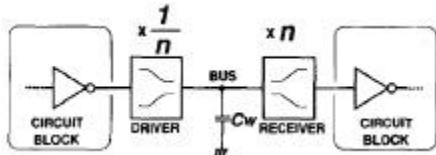

### 3.3.1 多電源形 [26]

Fig. 14 Architecture for internal bus swing reduction

本来の電源電圧よりも低い二つの電源を利用する方法である。Fig. 14 に回路図を示す。ドライバ回路でバス振幅を  $n$  分の 1 に変換し、レシーバ回路(レベルコンバータ)で元のフル振幅に戻す。本来の電源以外に二つの電源を供給しなければならないのが欠点である。

### 3.2.2 電荷再利用形 [27]

バスのあるビットの信号線が保有していた電荷を捨てないで別のビットの信号線に再利用する方法である。配線が  $n$  本あれば  $n$  本すべてに順々に電荷を再利用していくので最も優れた消費電力の削減法ではあるが、回路が非常に複雑になり面積ペナルティが大きい。

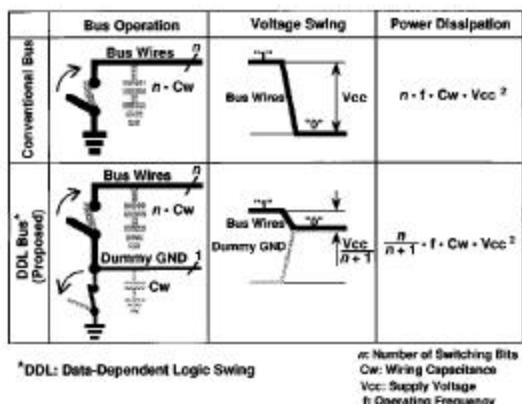

### 3.2.3 擬似接地形 [28]

Fig. 15 Basic concept of the conventional bus and the DDL Bus

バスの信号線に蓄えられた電荷をフローティング状態になった擬似的な接地線に流し込み電荷をバス信号線と

擬似接地線の容量に再分配させる方法である。基本的な概念図を Fig. 15 に示す。プリチャージ期間中にすべてのバスは電源レベル  $V_{CC}$  に充電され、擬似接地線は接地レベル  $V_{SS}$  に放電される。その後、擬似接地線を接地から切り離しバス線に接続すると、電荷はバス線と擬似接地線に分配され電位は  $1/(n+1) \times V_{CC}$  となり、 $n$  本のバスの消費電力は通常の  $1/(n+1)$  に抑えられる。しかし、バスの配線容量がばらつくとそれに依存して信号振幅もばらつくので全バスの配線長を等しくしなければならず、配置配線が難しくなる。

#### 4. メモリ部の低電圧技術

プロセッサ内に組み込まれるメモリとしては、レジスタファイル、キャッシュ、および仮想記憶システムの高速化のためのアドレス変換バッファ (TLB: Translation-Lookaside Buffer) がある。これらのメモリは論理回路部分と同等の高速性を要求されるので SRAM セルを用いる。SRAM の低消費電力化については多くの研究が成されているが[29]、ここではメモリセルの低電圧化についてのみ述べる。

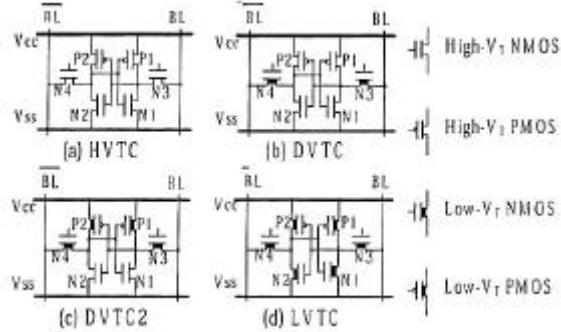

メモリ部のセルは低電圧・高速性を要求されるので通常完全 CMOS セルを用いるが、データの書き込み、読み出しの操作を伴うので論理回路部分より低電圧化は難しい。データラッチ部のトランジスタは完全にデータをストアするために High- $V_{TH}$  でなければならない。もし、Low- $V_{TH}$  だとプロセスによるしきい値ばらつきの結果ラッチ部でリークが起きデータを記憶できない可能性がある。また、通常ビット線には多くのセルが接続されており負荷容量が大きく充分な電力供給能力を必要とするので蓄えられるデータは高い電圧でなければならない。他にもワード線の駆動能力の問題などを考慮に入れると高速・低電圧の SRAM セルの実現は容易ではないが、0.5V 程度の低電圧化の挑戦がいくつか成されている。

#### 4.1 DSL (Driving Source Line Cell Architecture) [30]

メモリセルのソース線に負電圧をかける方式である。回路図を Fig. 16 に、ソースに-0.5Vを印加したときの従来のセルとの遅延の比較を Fig. 17 に示す。

Fig. 16 DSL cell

Fig. 17 Delay time

ソースに負電圧をかけることにより、ソース基盤間が順バイアスになり基盤バイアス効果でしきい値が減少して高速化できる。また、ノード電圧を低下させることができるので、ワード線駆動のパスゲートの実効的なゲート-ソース間電圧を上げることができる。Fig. 17 より  $V_{DD}=0.5V$  でも大きな遅延の増加はないことがわかる。

## 4.2 Multi-Threshold Cells

セル部分に High- $V_{TH}$  と Low- $V_{TH}$  のしきい値の異なる 2 種類のトランジスタを使う場合の様々なタイプのセルに関する比較研究が成されている。Fig. 18 に 6 個のトランジスタより成るいくつかのセル方式を示す[31]。消費電力の点からは High- $V_{TH}$  MOS だけのセル(a)が良いが、遅延の点では Low- $V_{TH}$  MOS だけのセル(d)が良い。そこで、消費電力・遅延積を考えると、パスゲートだけ Low- $V_{TH}$  MOS にしたセル(b)が最も優れているという結果が出されている。

Fig. 18 Different 6T SRAM Cell Designs

## 4.3 MTCMOS SRAM [32]

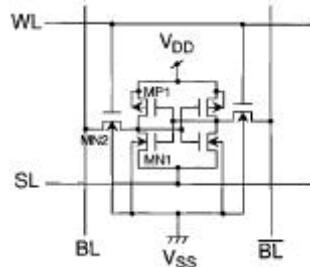

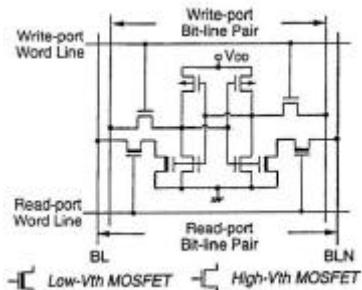

MTCMOS/SIMOX 技術を用いた 0.5-1V 動作の SRAM セルを紹介する。セル回路図を Fig. 19 に示す。

Fig. 19 The multi-Vth dual-port memory cell

データストア部と書き込み用のパストランジスタには High- $V_{TH}$  MOS( $V_{TH}=0.35V$ )が用いられ、読み出し用のトランジスタには Low- $V_{TH}$  MOS( $V_{TH}=0.15V$ )が用いられている。書き込み用と読み出し用のポートが分かれているのは、低電圧での読み出し誤りをなくすためである。Low- $V_{TH}$  MOS を用いているのでリーク電流を防ぐためビット線は Low にプリチャージされている。

$V_{DD}=0.5V$  で動作することが確認されており低消費電力を実現しているが、遅延は  $V_{DD}=1.0V$  の場合の 5 倍もあり高速化には難がある。また、ロープリチャージ方式では読み出し時にビット線の電位を引き上げなければならず大きなビット線負荷容量を充電するためには時間がかかるので良くない。

## 4.5 SRAM メモリセルの低電圧化の問題点

SRAM メモリセルの低電圧技術についていくつか紹介した。電源電圧を 0.5V に落とした場合、高速読み出しを

行うにはラッチ部の MOS のしきい値は 0.1-0.2V 程度に落とさなければならない。しかしリーク電流が発生し消費電力の増加につながってしまうので、ラッチ部の MOS は High- $V_{TH}$  MOS が望ましい。そうすると、 $V_{DD}=0.5V$  では動作しないので、ラッチ部の電源電圧を 1.0V 程度で用いる必要がある。この場合、書き込み時にはワード線もビット線も 1V にしなければならない。4.1 の DSL のようにソースを負電圧に引けば  $V_{DD}=0.5V$  も可能だが、トランジスタの酸化膜に大きな電界がかかり信頼性が低下する。結局のところ、現在のプロセス技術で用いるにはセル部分は  $V_{DD}=1.0V$  で周辺回路は  $V_{DD}=0.5V$  で動作させるのが妥当である。その際にはデコーダから出力された 0.5V 信号をいかに高速に 1.0V に変換するかが大きな問題となる。SRAM セルの高速を維持しながらの低電圧化は大きな困難を伴うと予測されるが、プロセッサの低電圧化・高速化に合わせるために必要不可欠である。

## 5. まとめと今後の展望

今後 10 年間程度のプロセッサ開発の中で、消費電力の増大を抑えるために必要になる低電圧技術について回路レベルで述べた。CMOS 回路の消費電力は通常、電源電圧の 2 乗に比例するので、電源電圧を低下させることが電力削減の最も効果的な方法である。しかし、同時にしきい値も下げる必要があり、低しきい値ではリーク電流が大きくなりかえって消費電力が増加してしまう。

そこで電源電圧としきい値を適切に制御して落とす必要がある。しきい値を制御する方法、また電源を制御する方法のそれぞれ主な技術を紹介した。現在では、高いしきい値の MOS をカットオフ MOS として用い論理回路部分は低いしきい値の MOS で構成する MTCMOS がよく使われている。また、 $V_{DD}=1V$  以下の低電圧技術として SCCMOS、BGMOS などが考案されている。電源電圧を要求される周波数に合わせて動的に変える方法は一部の低消費電力プロセッサで使用されている。SRAM メモリ部に関しては現在はすべてを  $V_{DD}=0.5V$  にするのは難しく、セル部は  $V_{DD}=1V$ 、周辺回路は  $V_{DD}=0.5V$  で用いるのが良いと考えられる。

プロセッサの高速化は現在もなお速い速度で進んでいるが消費電力が大きくなりすぎると、携帯機器に組み込めない可能性も出てくる。2011 年には 0.5V, 10GHz 動作のプロセッサが開発されると予測されているが、その実現にはプロセス、回路両面から大きな困難が予想される。将来すべてのプロセッサが 10GHz もの高速で動作する必要はなく用途、実装形態に応じて高パフォーマンス用と低電力用への分化が進んでいくだろう。むしろ、通常の用途では現在のプロセッサですでに充分に高速であるといえるので、現在のパフォーマンスを維持しながら低電圧化する方が、将来大きな発展が期待される携帯機器への組み込みが可能になるという点で有意義であると思われる。

## Reference

[1] F. Federico, H. Marcian. E Jr., M. Stanley, S. Masatoshi, "History of the 4004", IEEE Micro., Vol.16, No.6, pp.10-20. Dec., 1996

[2] "International Technology Roadmap for Semiconductors 1999 edition", Semiconductor Industry Association

[3] Hiroshi iwai, "CMOS Technology – Year 2010 and Beyond", IEEE J.Solid-State Circuits, vol.34, No.3, pp.357-366, Mar., 1999

[4] "Mobile Pentium III Processor in BGA2 and Micro-PGA2 Packages Datasheet", <http://www.intel.com/>

[5] "Mobile Power Guidelines Rev. 1.00", <http://www.intel.com/>

[6] "The Technology Behind Crusoe Processors", <http://www.transmeta.com/>

[7] R. Gonzalez, B.M. Gordon, and M.A. Horowitz, "Supply and Threshold Voltage Scaling for Low Power CMOS", IEEE J.Solid-State Circuits, vol.32, No.8, pp.1210-1216, Aug., 1997

[8] A.P. Chandrakasan, S. Sheng, and R.W. Brodersen, "Low-Power CMOS Digital Design", IEEE J.Solid-State Circuits, vol.27, No.4, pp.473-482, Apr., 1992

[9] Gary K. Yeap, "Practical Low Power Digital VLSI Design", Kluwer Academic Publishers

[10] "PowerPC 750 RISC Microprocessor Technical Summary", <http://www.chips.ibm.com/>

[11] S. Lee and T. Sakurai, "Run-time Power Control Scheme using Software Feedback Loop for Low-Power Real-time Applications", Proceedings of ASP-DAC'00, 2000

[12] R. Zimmermann and W. Fichtner, "Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic", IEEE J.Solid-State Circuits, vol.32, No.7, pp.1079-1090, Jul., 1997

[13] T. Sakurai and A.R. Newton, "Alpha-power law MOSFET model and its application to CMOS inverter delay and other formulas", IEEE J.Solid-State Circuits, vol.25, No.2, pp.584-594, Apr., 1990

[14] T. Kuroda and T. Sakurai, "Overview of low-power ULSI circuit techniques", IEICE Trans. on Electronics, E78-C, Vol.4, pp.334-344, Apr., 1995

[15] T. Kuroda and T. Sakurai, "Low-Voltage Technologies and Circuits", IEEE press, Low-Power CMOS Design, pp.61-65

[16] T. Wang, L.P. Chiang, N.K. Zous, "A Comprehensive Study of Hot Carrier Stress-Induced Drain Leakage Current Degradation in Thin-Oxide n-MOSFET's", IEEE Trans. on Electron Devices, vol.46, No.9, pp.1877-1882, Sep., 1999

Charng-Feng Hsu, Li-Yuan Huang, and Tien-Sheng Chao

[17] S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, and J. Yamada, "1-V Power Supply High-Speed Digital Circuit Technology with Multithreshold-Voltage CMOS", IEEE J.Solid-State Circuits, vol.30, No.8, pp.847-854, Aug., 1995

[18] S. Shigematsu, S. Mutoh, Y. Matsuya, Y. Tanabe and J. Yamada, "A 1-V High-Speed MTCMOS Circuit Scheme for Power-Down Application Circuits", IEEE J.Solid-State Circuits, vol.32 No.6 pp.861-869, Jun., 1997

[19] T. Kuroda, T. Fujita, S. Mita, T. Nagamatsu, S. Yoshioka, K. Suzuki, F. Sano, M. Norishima, M. Murota, M. Kato, M. Kinugawa, M. Kakumu, and T. Sakurai, "A 0.9-V, 150-MHz, 10-mW, 4mm<sup>2</sup>, 2-D Discrete Cosine Transform Core Processor with Variable Threshold-Voltage(VT) Scheme", IEEE J.Solid-State Circuits, vol.31, No.11, pp.1770-1779, Nov., 1996

[20] H. Kawaguchi, K. Nose, and T. Sakurai, "A Super Cut-Off CMOS (SCCMOS) Scheme for 0.5-V Supply Voltage with Picoampere Stand-By Current", IEEE J.Solid-State Circuits, vol.35, No.10, pp.1498-1501, Oct., 2000

[21] T. Inukai, M. Takamiya, K. Nose, H. Kawaguchi, T. Hiramoto and T. Sakurai, "Boosted Gate MOS (BGMOS): Device/Circuit Cooperation Scheme to Achieve Leakage-Free Giga-Scale Integration", IEEE 2000 Custom Integrated Circuits Conference, pp. 409-412, May, 2000

[22] J.T. Kao and A.P. Chandrakasan, "Dual-Threshold Voltage Techniques for Low-Power Digital Circuits", IEEE J.Solid-State Circuits, vol35, No.7, pp.1009-1018, Jul., 2000

[23] T. Yamashita, N. Yoshida, M. Sakamoto, T. Matsumoto, M. Kosunoki, H. Takahashi, A. Wakahara, T. Ito, T. Shimizu, K. Kurita, K. Higota, K. Mori, N. Tamba, N. Kato, K. Miyamoto, R. Yamagata, H. Tanaka, T. Hirayama, "A 450MHz 64b RISC Processor using Multiple Threshold Voltage CMOS", IEEE International Solid-State Circuits Conference, pp.414-415, 2000

[24] K. Usami, K. Nogami, M. Igarashi, F. Minami, Y. Kawasaki, T. Ishikawa, M. Kanazawa, T. Aoki, M. Takano, C. Mizuno, M. Ichida, S. Sonoda, M. Takahashi and N. Hatanaka, "Automated Low-power Technique Exploiting Multiple Supply Voltages Applied to a Media Processor", IEEE Custom Integrated Circuits Conference, pp.131-134, 1997

[25] K. Suzuki, S. Mita, T. Fujita, F. Yamane, F. Sano, A. Chiba, Y. Watanabe, K. Matsuda, T. Maeda and T. Kuroda, "A 300MIPS/W RISC Core Processor with Variable Supply-Voltage Scheme in Variable Threshold-Voltage CMOS", IEEE Custom Integrated Circuits Conference, pp.587-590, 1997

[26] Y. Nakagome, K. Itoh, M. Isoda, K. Takeuchi, and M. Aoki, "Sub-1-V Swing Internal Bus Architecture for Future Low-Power ULSI's", IEEE J.Solid-State Circuits, vol.28, No.4, pp.414-419, Apr., 1993

[27] H. Yamauchi, H. Akamatsu and T. Fujita, "A Low Power Complete Charge-Recycling Bus Architecture for Ultra-High Data Rate ULSI's", Symposium on VLSI Circuit Digest of Technical Papers, 1994

[28] M. Hiraki, H. Kojima, H. Misawa, T. Akazawa, and Y. Hatano, "Data-Dependent Logic Swing Internal Bus Architecture for Ultralow-Power LSI's", IEEE J.Solid-State Circuits, vol.30, No.4, pp.397-402, Apr., 1995

[29] B.S. Amrutur and M.A. Horowitz, "Speed and power Scaling of SRAM's", IEEE J.Solid-State Circuits, vol.35, No.2, pp.175-185, Feb., 2000

[30] H. Mizuno and T. Nagano, "Driving Source-Line Cell Architecture for Sub-1-V High-Speed Low-Power Applications", IEEE J.Solid-State Circuits, vol.31, No.4, pp.552-557, Apr., 1996

[31] F. Hamzaoglu, Y. Ye, A. Keshavarzi, K. Zhang, S. Narendra, S. Borkar, M. Stan and V. De, "Dual- V<sub>T</sub> SRAM Cells with Full-Swing Single-Ended Bit Line Sensing for High-Performance On-Chip Cache in 0.13um Technology Generation", International Symposium on Low Power Electronics and Design, pp.15-19, 2000

[32] T. Douseki, N. Shibata and J. Yamada, "A 0.5-1V MTCMOS/SIMOX SRAM Macro with Multi-V<sub>th</sub> Memory Cells", IEEE International SOI Conference, 2000