# 低振幅ビット線方式を用いた低消費電力高速 SRAM

Low-power high-speed SRAM circuits using low-swing bit-lines

・服部 貞昭

Sadaaki Hattori

東京大学生産技術研究所

桜井 貴康

Takayasu Sakurai

Institute of Industrial Science, University of Tokyo

## 1. はじめに

論理部の低消費電力化手法としてよく電源電圧としきい値を適切に低減させる方法がとられる。しかし、SRAMの場合、論理部と同じように、単に電源電圧としきい値を下げる最適化はすることはできない。電源電圧を単に落とせば書き込みおよび読み出しの遅延が大きくなるし、またしきい値を落とせばリーク電流が大きくなる。

現在の SRAM では書き込みを行う前にまずプリチャージで両方のビット線の電位を電源電圧  $V_{DD}$  まで引き上げるが、ビット線の容量は大きいのでここで大きな電力を消費する。そこで、ビット線のプリチャージレベルを  $V_{DD}/2$  にすることで書き込み時の消費電力を理論的に半減させる Half-swing 方式[1]がある。しかし、この方式では破壊読み出しのおそれがあり、また消費電力をさらに削減することはできない。そこで、低振幅のビット線で書き込みを行い消費電力を大幅に削減する方法を提案する。

## 2. 低振幅ビット線方式 (Low-swing 方式)

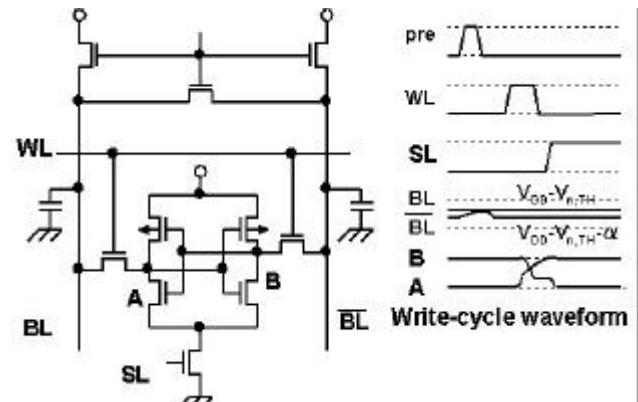

通常の 6Tr. の SRAM セルの nMOS ドライバのソース側に nMOS スイッチを付加することで低振幅ビット線による SRAM セルの書き込み(以下、Low-swing 方式と呼ぶ)を実現した。その回路図および書き込み動作の信号波形を Fig. 1 に示す。

書き込む前にまずプリチャージを行う。nMOS 負荷でプリチャージされるので、ビット線電位は  $V_{DD}-V_{TH}$  となる。次に片方のビット線の電位を  $V_{DD}-V_{TH}-\alpha$  まで下げる。の値は  $0.15V \sim 0.30V$  くらいを想定している。ここでワード線(WL)を開けて書き込むのだが、ビット線間の振幅差が小さいとドライバの駆動力の方が強くノードの電位は反転しない。そこで、ドライバのソース側に付加した nMOS スイッチをあらかじめ切ってから、ワード線を開ける。すると、ノード電位はなれば浮いた状態になるので反転させることができる。反転して二つのノード間の電位差が充分にいたらワード線を切り nMOS スイッチを開ける。

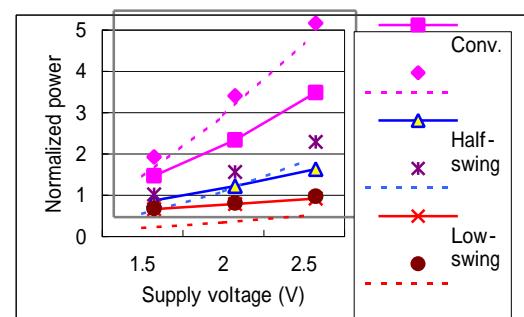

Low-swing 方式では、書き込みを終えたあとの次の動作でのプリチャージにかかる消費電力を大幅に削減できるので、書き込み読み出しの連続したサイクルで消費電力を大きく削減できるという利点がある。従来の SRAM セル及び Half-swing 方式、Low-swing 方式の 3 方式の消費電力の HSPICE シミュレーションを行った結果を図 2 に示す。実線は書き込み読み出しサイクルにおける消費電力、点線は連続した書き込み書き込みサイクルにおける消費電力を示している。提案する Low-swing 方式の場合、 $V_{DD}=1.5V$  の書き込み読み出しサイクルの消費電力は、従来の方式より 5 分の 1 に削減されることが確認された。

SRAM セル部のみのチップの試作を表 1 の仕様で行った。今後、測定評価する予定である。

## 3. まとめ

低振幅ビット線を用いて低消費電力で SRAM の書き込みを行う方式を提案し、チップの試作を行った。

## 参考文献

- [1] Kenneth W. Mai, Toshihiko Mori, Bharadwaj S. Amrutur, Ron Ho, Bennett Wilburn, Mark, A. Horowitz, Isao Fukushi, Tetsuo Izawa, and Shin Mitarai, "Low-Power SRAM Design Using Half-Swing Pulse-Mode Techniques", IEEE J. Solid-State Circuits, vol.33, No.11, pp.1659-1671, Nov., 1998

図 1 Low-swing 方式の SRAM セル回路図および書き込み動作の信号波形

図 2 3 つの方式の消費電力の比較

|                |                            |

|----------------|----------------------------|

| Technology     | 0.35μm CMOS 3-metal (Rohm) |

| Organization   | 256 × 256 cells            |

| Supply voltage | 1.5V ~ 2.5V                |

| Core size      | 4.0mm <sup>2</sup>         |

| Cell size      | 55.3μm <sup>2</sup>        |

表 1 試作した SRAM セルの仕様