# 高速レベルコンバータ

High-speed level converter

東京大学生産技術研究所 服部 貞昭 神田 浩一 桜井 貴康

IIS, University of Tokyo Sadaaki Hattori Kouichi Kanda Takayasu Sakurai

hat@iis.u-tokyo.ac.jp kouichi@iis.u-tokyo.ac.jp tsakurai@iis.u-tokyo.ac.jp

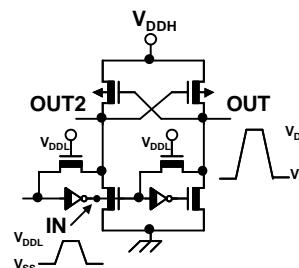

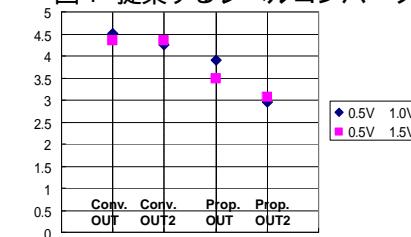

LSI の消費電力を削減するために論理部の電源の低電圧化がすすんでいるが、一方で電圧を著しく下げる事でのきない回路や I/O が存在するために、低い信号電圧を高い電圧に変換するためのレベルコンバータが必要とする。すでに様々なタイプのレベルコンバータが研究されているが[1]、低電圧を高電圧に高速に変換することは難しい。さらに、次世代の 0.5V 程度の極小電圧を高い電圧に変換するコンバータについてはまだ充分な評価が成されていない。そこで極小電圧の高速レベルコンバータを提案する。その回路図を図 1 に示す。極小電圧を扱うために低いしきい値の MOS を用いている。通常のクロスカッフル型のレベルコンバータに nMOS を二つ付加した。IN から入力された低電圧  $V_{DDL}$  が高電圧  $V_{DDH}$  に変換され OUT より出力される。付加した nMOS はその両端のノード電圧が  $V_{DDL}-V_{TH}$  ( $V_{TH}$ : しきい値電圧) 以下の時は ON して入力と出力が短絡され出力の遅延が小さくなる。一方で、nMOS の両端のノード電圧が  $V_{DDL}-V_{TH}$  以上の時は OFF するので入出力間が短絡される心配はない。従来のレベルコンバータと nMOS を付加したコンバータについて、入力に NAND を出力にインバータを付加し、HSPICE シミュレーションで遅延の比較をした結果を図 2 に示す。 $V_{DDL}=0.5V$  をそれぞれ  $V_{DDH}=1.0V$  および  $V_{DDH}=1.5V$  に変換する場合について検討したが、どちらの場合も従来のコンバータより遅延が改善されている。また、図 1 において通常使用される OUT 端子を出力とするよりも OUT2 端子を出力とする方が遅延はより少ないとても明らかになった。

[1] Hui Zhang, Jan Rabaey, "Low-Swing Interconnect Interface Circuits", International Symposium on Low Power Electronics and Design, pp.161-166, 1998

図 1 提案するレベルコンバータ

図 2 遅延特性の比較